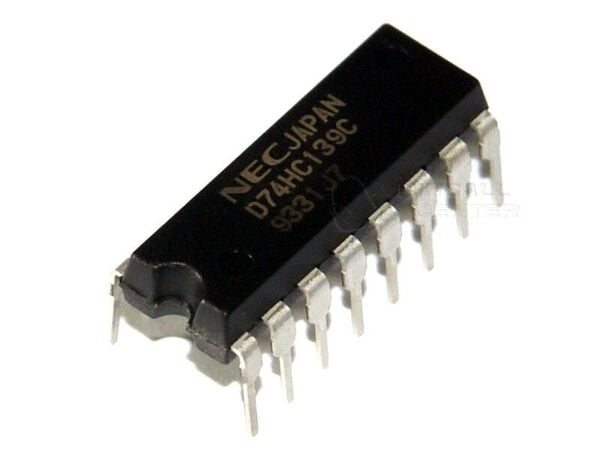

IC 74139 (3 to 8 Line Decoder IC)

1.300BD

IC 74139 (3 to 8 line decoder IC) is designed to provide a reliable and efficient decoding solution for your needs. With a high-quality IC and a durable design, this module is perfect for use in various applications, including electronics and engineering.

Choose Quantity

Product Details

Electronics and Components

Usage scenarios:

Features:

• High-quality IC

• 3 to 8 configuration

• Decoder configuration

Usage scenarios:

• Decoding data

• Improving system performance

• Enhancing user experience

• Creating efficient decoding systems